Dipl.-Ing. Mario Schenk

## AnSim: An Analytic Simulator for Electronic Circuits

#### DISSERTATION

to obtain the university degree of Doktor der technischen Wissenschaften (Dr. techn.)

submitted to

#### Graz University of Technology, Austria

Supervisor and First Assessor:

Prof. Annette Mütze Electric Drives and Machines Institute, Graz University of Technology, Austria

Second Assessor:

Prof. Hans-Peter Nee Division of Electric Power and Energy Systems, KTH Royal Institute of Technology, Sweden

Graz, November 2020

#### AFFIDAVIT

I declare that I have authored this thesis independently, that I have not used other than the declared sources/resources, and that I have explicitly indicated all material which has been quoted either literally or by content from the sources used. The text document uploaded to TUGRAZonline is identical to the present doctoral thesis.

Date

Signature

# Contents

| Та | Table of contentsi                                                                                  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |  |

|----|-----------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| A  | bstra                                                                                               | ct        | sixn1adard simulators which use complex nonlinear models3ulators based on switched networks with piecewise-linear4dels4ded approach4deling of the circuit elements' parameters6mple case worst-case diode forward voltage model8art11adard approach(es)11e-space equation approach13er approaches15lications16of the thesis16of the thesis16of solver approach for solving electronic circuits19erview23ubCircuit-Model of an electronic circuit25eral form of a SubCircuit-Model26litional information of a SubCircuit-Model27 |    |  |

| Zı | bstract v<br>usammenfassung (in German) vii<br>cknowledgements ix<br>Overview 1<br>1.1 Introduction |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |  |

| A  | cknov                                                                                               | wledge    | ments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ix |  |

| 1  | Ove                                                                                                 | erview    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  |  |

|    | 1.1                                                                                                 | Introc    | luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1  |  |

|    |                                                                                                     | 1.1.1     | Standard simulators which use complex nonlinear models                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3  |  |

|    |                                                                                                     | 1.1.2     | Simulators based on switched networks with piecewise-linear                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |

|    |                                                                                                     |           | models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4  |  |

|    | 1.2                                                                                                 | The p     | roposed approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4  |  |

|    |                                                                                                     | 1.2.1     | Modeling of the circuit elements' parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6  |  |

|    |                                                                                                     | 1.2.2     | Example case worst-case diode forward voltage model                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8  |  |

|    | 1.3                                                                                                 | State     | of the art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 |  |

|    |                                                                                                     | 1.3.1     | Standard approach(es)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11 |  |

|    |                                                                                                     | 1.3.2     | State-space equation approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13 |  |

|    |                                                                                                     |           | * *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15 |  |

|    | 1.4                                                                                                 | List of   | f publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 |  |

|    | 1.5                                                                                                 | Overv     | view of the thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16 |  |

| 2  | Ana                                                                                                 | alytic fo | orward solver approach for solving electronic circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19 |  |

|    | 2.1                                                                                                 | Metho     | od overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23 |  |

|    | 2.2                                                                                                 | Propo     | sed SubCircuit-Model of an electronic circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25 |  |

|    |                                                                                                     | 2.2.1     | General form of a SubCircuit-Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25 |  |

|    |                                                                                                     | 2.2.2     | Interconnection of SubCircuit-Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26 |  |

|    |                                                                                                     | 2.2.3     | Additional information of a SubCircuit-Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27 |  |

|    | 2.3                                                                                                 | Circui    | it-Model of an electronic circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27 |  |

|   |     | 2.3.1   | General form of a Circuit-Model                                 | 27 |

|---|-----|---------|-----------------------------------------------------------------|----|

|   |     | 2.3.2   | Boundary conditions of the Circuit-Model                        | 28 |

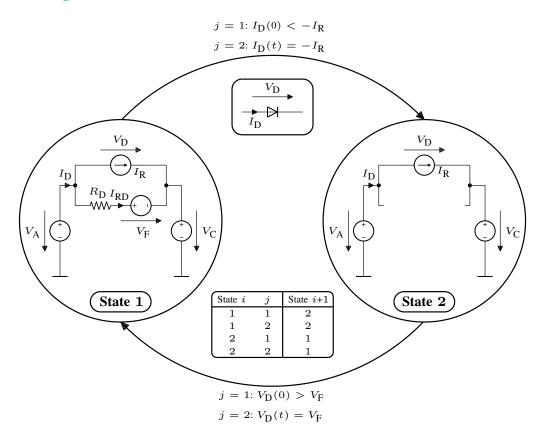

|   |     | 2.3.3   | State control of the Circuit-Model                              | 28 |

|   |     | 2.3.4   | Interconnection of Circuit-Models                               | 29 |

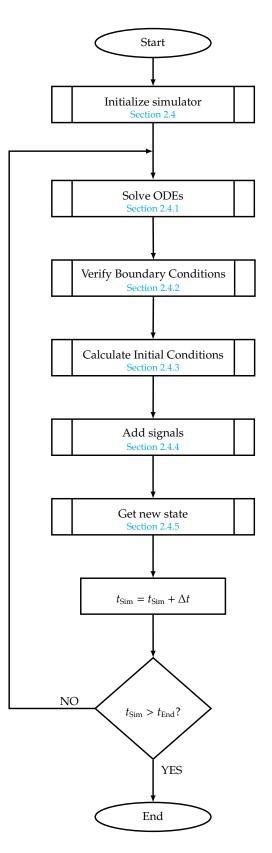

|   | 2.4 | Transi  | ient analysis                                                   | 30 |

|   |     | 2.4.1   | ODE system solver module                                        | 30 |

|   |     | 2.4.2   | Boundary condition module                                       | 30 |

|   |     | 2.4.3   | Initial condition module                                        | 31 |

|   |     | 2.4.4   | Signal module                                                   | 31 |

|   |     | 2.4.5   | State module                                                    | 32 |

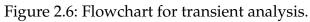

|   | 2.5 | Optin   | nization and worst-case analysis of electronic circuits         | 34 |

|   |     | 2.5.1   | SQP approach                                                    | 34 |

|   |     | 2.5.2   | SQP iteration in case of active constraints                     | 36 |

|   |     | 2.5.3   | SQP iteration in case of no active constraints                  | 37 |

|   |     | 2.5.4   | SQP method inverse Hessian update                               | 37 |

|   |     | 2.5.5   | SQP implementation                                              | 37 |

| _ | _   | _       |                                                                 |    |

| 3 |     | -       | ases and experimental validation of the analytic forward solver |    |

|   |     | roach   |                                                                 | 41 |

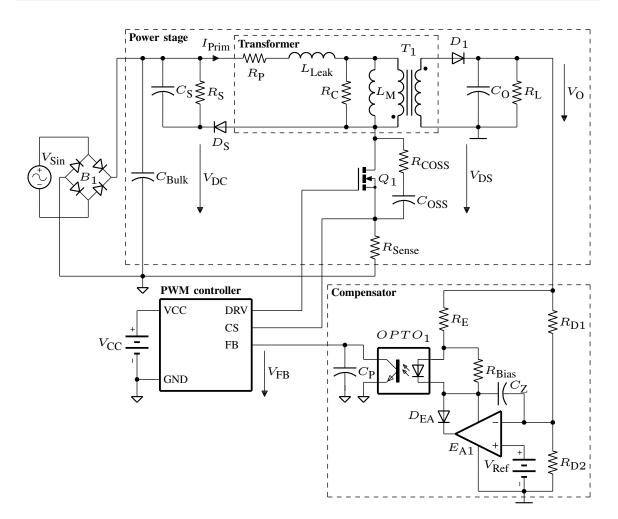

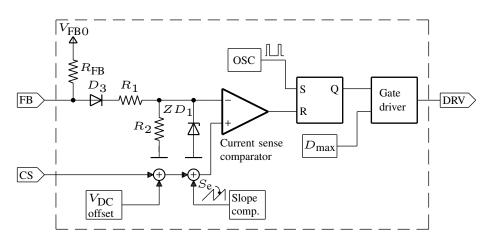

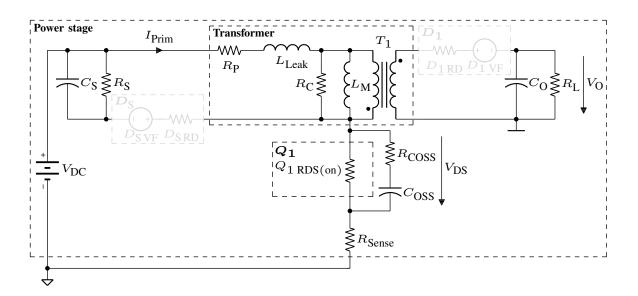

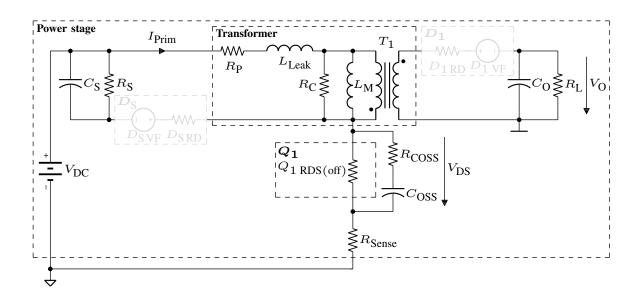

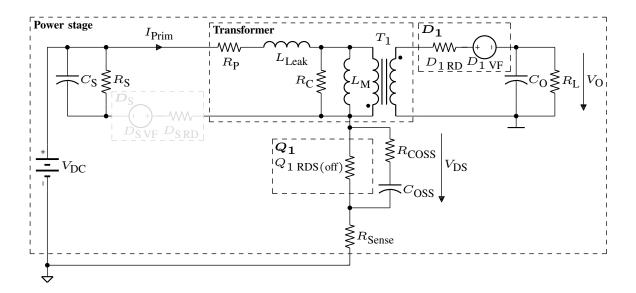

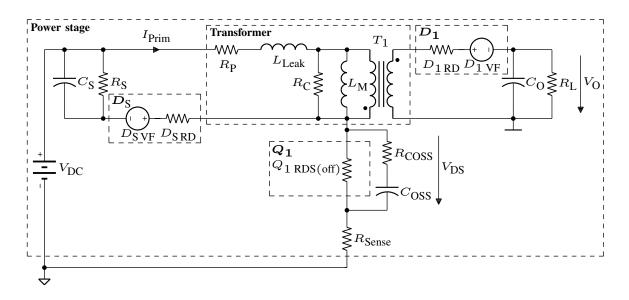

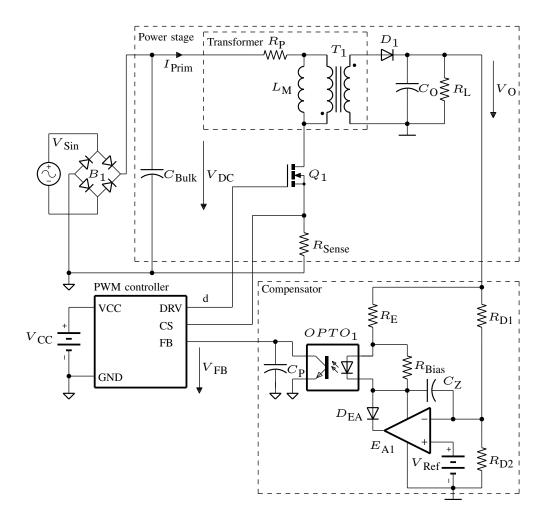

|   | 3.1 |         | ple case flyback converter                                      | 41 |

|   |     | 3.1.1   | Open-loop flyback converter in steady-state                     | 42 |

|   | ~ ~ | 3.1.2   | Closed-loop flyback converter during start-up                   | 44 |

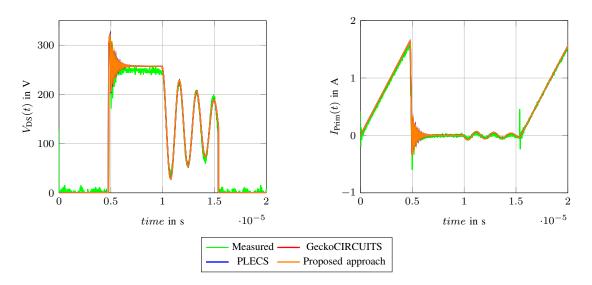

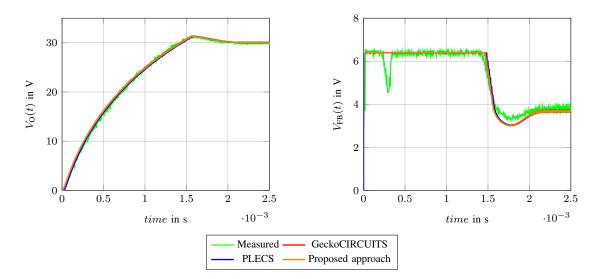

|   | 3.2 | Result  |                                                                 | 45 |

|   |     | 3.2.1   | Results open-loop flyback converter in steady-state             | 45 |

|   |     | 3.2.2   | Results closed-loop flyback converter during start-up           | 50 |

|   |     | 3.2.3   | 1                                                               | 51 |

|   | 3.3 | Concl   | usion                                                           | 52 |

| 4 | Exa | mple ca | ases for worst-case analyses                                    | 53 |

|   | 4.1 | Worst   | -case analysis of an RLC series resonant circuit                | 53 |

|   |     | 4.1.1   | SubCircuit-Model of an RLC series resonant circuit              | 53 |

|   |     | 4.1.2   | Analytic analysis of an RLC series resonant circuit             | 54 |

|   |     | 4.1.3   | Worst-case analysis of an RLC series resonant circuit           | 54 |

|   | 4.2 | Worst   | -case analysis of a second flyback converter in continuous con- |    |

|   |     |         | on mode                                                         | 57 |

|   |     | 4.2.1   | Steady-state analysis                                           | 58 |

|   |     | 4.4.1   |                                                                 | 00 |

|    |       | 4.2.2          | SQP result                                                                     | 61 |

|----|-------|----------------|--------------------------------------------------------------------------------|----|

|    |       | 4.2.3          | Transient simulation                                                           | 62 |

|    |       | 4.2.4          | Performance comparison                                                         | 62 |

|    |       | 4.2.5          | A more complex example case                                                    | 64 |

|    | 4.3   | Concl          | usion                                                                          | 64 |

| 5  | Exa   | mple ca        | ase sizing of a step down converter                                            | 65 |

|    | 5.1   | Specif         | ication and requirements of the step down converter                            | 66 |

|    | 5.2   | Power          | r stage modeling of the step down converter                                    | 66 |

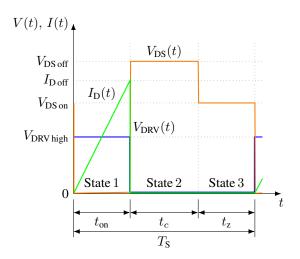

|    |       | 5.2.1          | Steady-state analysis                                                          | 67 |

|    |       | 5.2.2          | Modeling of the switching losses of the MOSFET $Q_1 \ldots \ldots$             | 68 |

|    |       | 5.2.3          | Efficiency calculation                                                         | 70 |

|    |       | 5.2.4          | Calculation of the junction temperature of the MOSFET $Q_1$                    | 71 |

|    |       | 5.2.5          | Calculation of the average forward current of the Diode $D_1$ .                | 71 |

|    |       | 5.2.6          | Calculation of the junction temperature of the Diode $D_1$                     | 72 |

|    |       | 5.2.7          | Calculation of the ripple current of the output capacitor $C_{\rm O}$ .        | 72 |

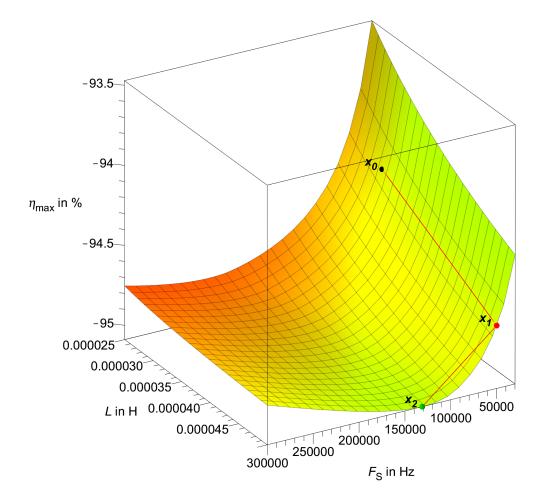

|    | 5.3   | Optin          | nization of the efficiency of the step down converter                          | 72 |

|    | 5.4   | Desig          | n limits of the individual components                                          | 75 |

|    |       | 5.4.1          | Design limits of the MOSFET $Q_1$                                              | 76 |

|    |       | 5.4.2          | Design limits of the diode $D_1$                                               | 76 |

|    |       | 5.4.3          | Design limits of the output capacitor $C_0 \ldots \ldots \ldots \ldots \ldots$ | 77 |

|    | 5.5   | Concl          | usion                                                                          | 78 |

| 6  | Con   | clusio         | ı                                                                              | 79 |

|    | 6.1   | Summ           | nary                                                                           | 79 |

|    | 6.2   | Future         | ework                                                                          | 81 |

| Bi | bliog | graphy         |                                                                                | 83 |

| A  | Step  | o down         | converter SQP iterations of the individual components                          | 91 |

| В  | Sem   | nicondi        | actor modeling                                                                 | 97 |

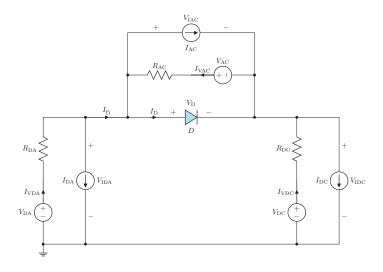

| D  | B.1   | Diode          |                                                                                | 97 |

|    | J.1   | B.1.1          | Diode model parameters                                                         | 98 |

|    |       | B.1.1<br>B.1.2 | Diode I/O interface                                                            | 99 |

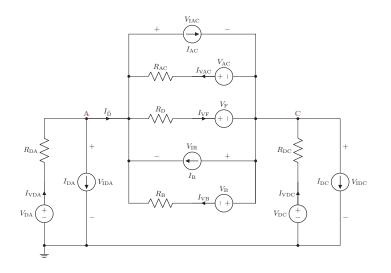

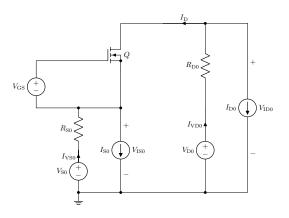

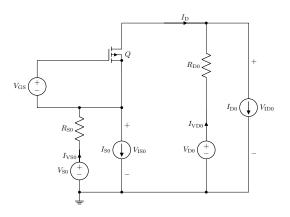

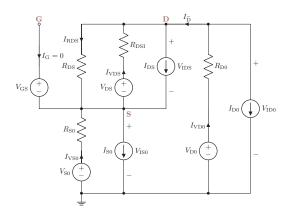

|    | B.2   |                | FET   ····································                                     | 99 |

|    | 1.2   | B.2.1          | MOSFET model parameters                                                        | 99 |

|    |       | 1.2.1          |                                                                                | ,, |

|     | B.2.2 | MOSFET I/O interface       | 101 |

|-----|-------|----------------------------|-----|

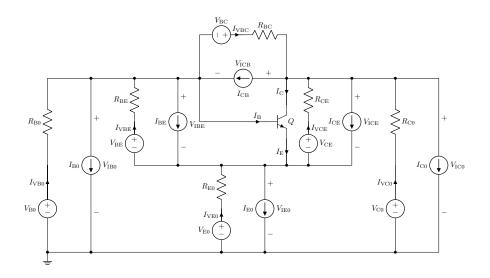

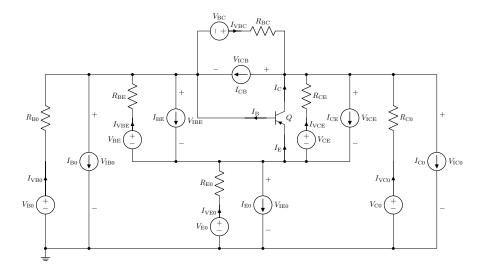

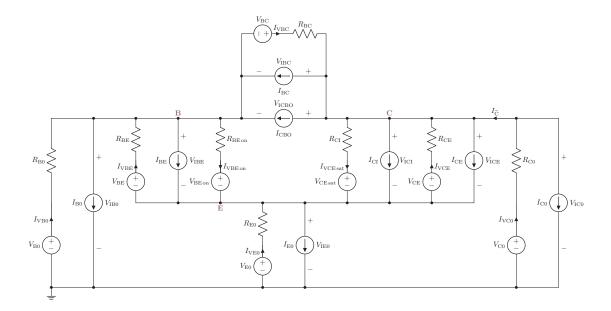

| B.3 | BJT   |                            | 102 |

|     | B.3.1 | BJT model parameters       | 103 |

|     | B.3.2 | BJT I/O interface          | 105 |

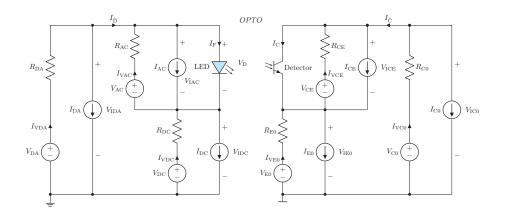

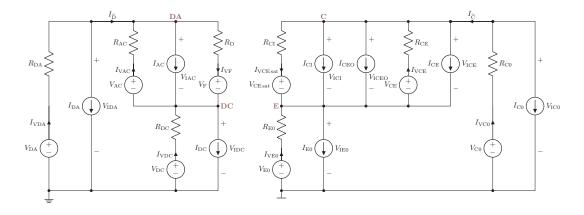

| B.4 | Optoc | coupler                    | 105 |

|     | B.4.1 | OPTO model parameters      | 106 |

|     | B.4.2 | Optocoupler I/O interface  | 107 |

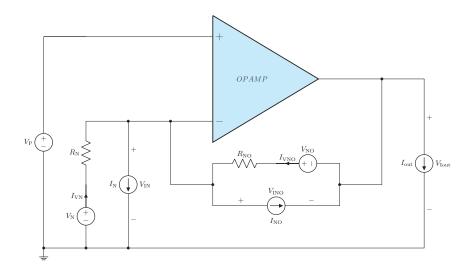

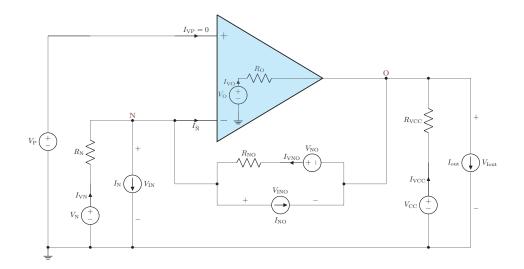

| B.5 | Ampl  | ifier OPAMP                | 107 |

|     | B.5.1 | Amplifier model parameters | 107 |

|     | B.5.2 | Amplifier I/O interface    | 109 |

|     |       |                            |     |

## Abstract

In many fields of electronics, the number of competitors continues to be on the rise. Shortening the market launch, the so-called time to market (TTM), is therefore essential when gaining an advantage over the competition. The electronic development (from prototype to the final design) shall be as efficient as possible. A wide range of applications needs electronic circuits, e.g., from simple analog circuits to switch mode power supplies. The specification (functions or requirements for the circuit design) must be met over the entire product lifetime. In addition to the ambient conditions during operation, additional influencing factors such as component tolerances and component aging have to be taken into account. Electronic circuits can be designed by calculation and/or simulation, respectively. The most efficient method would be to compute the circuit (i.e., by an equation for the function or the worst-case values, and also using mathematical operations directly). However, this is not always possible for reasons of complexity.

The aim of this thesis is to develop a tool for the design of electronic circuits and, most notably, for the sizing of the components that can be used as universally as possible, which supports calculation as well as simulation. Its central element is the development of an analytic forward solver. The electronic circuit is described by switched networks with piecewise-linear models (symbolic state-space equations). A closed-form analytic solution is computed for each model. The advantages of this analytic approach are: no convergence problems (since no numerical integration is required), high simulation speed (especially for small-scale electronic circuits), high accuracy, as well as small data file sizes. In many cases, the exact signal waveforms are not required for the calculation (e.g., forward voltage of a diode as a function of the current), only the minimum and maximum values (to determine if the function or the component specification is fulfilled). More complex electronics circuits are realized by several simpler models. Therefore, even complex electronics circuits can be modeled and analyzed relatively easily. In particular, the sensitivity of an output variable/performance parameter with respect to individual parameters, e.g.,

through a parameter variation can be analyzed.

# Zusammenfassung

In vielen Bereichen der Elektronik nimmt die Anzahl der Wettbewerber immer mehr zu. Eine Verkürzung der Markteinführungszeit, die sogenannte Time-to-Market (TTM), ist daher wesentlich, um Wettbewerbsvorteile gegenüber der Konkurrenz zu erzielen. Das Ziel ist es, die Elektronikentwicklung (vom Prototypen bis zum finalen Design) möglichst effizient zu gestalten. Ein großer Bereich der Anwendungen benötigt elektronische Schaltungen, angefangen von einfachen analogen Schaltungen hin bis zu getakteten Stromversorgungen. Dabei muss garantiert werden, dass die Spezifikation (Funktionen bzw. Anforderungen an das Schaltungsdesign) über die gesamte Produktlebensdauer eingehalten wird. Es müssen neben den Umweltbedingungen im Betrieb noch zusätzliche Einflussfaktoren wie Bauteiltoleranzen und Bauteilalterung berücksichtigt werden. Die Dimensionierung einer elektronischen Schaltung kann durch Berechnung und/oder Simulation erfolgen. Die effizienteste Methode wäre die Berechnung (eine Formel für die Funktion oder der Worst-Case-Werte und des Weiteren auch die direkte Anwendung von mathematischen Operationen ermöglichen) der elektronischen Schaltung, was jedoch aus Komplexitätsgründen nicht immer möglich ist.

Das Ziel dieser Dissertation ist es, ein möglichst universal einsetzbares Dimensionierungstool zu entwickeln, welches sowohl Berechnung als auch Simulation unterstützt. Ein wesentlicher Bestandteil dieser Arbeit ist die Entwicklung eines analytischen Vorwärtslösers. Die elektronische Schaltung wird durch geschaltete lineare Netzwerke mit stückweise linearen Modellen (symbolische Zustandsraumgleichungen) beschrieben. Für jedes Modell wird eine analytische Lösung in geschlossener Form berechnet. Die Vorteile dieses analytischen Ansatzes sind: Keine Konvergenzprobleme (da keine nummerische Integration erforderlich), hohe Simulationsgeschwindigkeit (insbesondere bei kleinen elektronischen Schaltungen), hohe Genauigkeit, sowie eine geringe Datengröße der Dateien. Da in vielen Fällen für die Berechnung nicht die exakten Signalverläufe (z.B. Vorwärtsspannung einer Diode in Abhängigkeit des Stromes) benötigt werden, sondern nur Min- und Max-Werte

(um zu bestimmen, ob die Funktion bzw. Bauteilspezifikation eingehalten wird), ist dieser Ansatz möglich. Komplexere elektronische Schaltungen werden durch mehrere einfachere Modelle realisiert. Dadurch können auch komplexere elektronische Schalungen relativ einfach modelliert und analysiert werden. Insbesondere können die Sensitivität einer Ausgangsgröße/eines Performanceparameters gegenüber einzelner Parameter z.B. durch eine Parametervariation beurteilt werden.

# Acknowledgements

At this point I would like to express a big thank you to everyone who supported me by creating this thesis and special thanks to Univ.-Prof. Dr.-Ing. Annette Mütze, Prof. Hans-Peter Nee, Ass.Prof. Dipl.-Ing. Dr.techn. Klaus Krischan, and Ao.Univ.-Prof. Dipl.-Ing. Dr.techn. Christian Magele.

My sincere thanks go to Dipl.-Ing. Walter Koch and Dipl.-Ing. (FH) Stefan Lukas who have given me the opportunity to conduct this research and who made this thesis possible in cooperation with the company Logicdata.

The biggest thanks go to my family, especially my wife and my children for always supporting me.

## Chapter 1

### Overview

#### 1.1 Introduction

Today, virtual prototyping is the most efficient way for the development of electronic apparatuses. Electronic components always come with certain tolerances; therefore, the sizing of the electronic circuits to consider the worst-case (extreme) values of the different parameters<sup>1</sup>, i.e., worst-case sizing of electronic circuits composed of such components, has been gaining more and more in importance. Two essential aspects must be considered: the specification of the device (must be met), and the components are not allowed to be overloaded. This can be succinctly summarized as the design limits of the device and the design limits of the individual components, respectively. The design limits of the device must be determined by the ranges of the components' parameters<sup>2</sup> (so-called worst-case parameter models) and need to stay below the pre-defined limits, e.g., current and voltage limits mainly defined in the specification of the electronic apparatuses. The design limits of the individual components are determined (considering the ranges of the components' parameters, too) and should never exceed the defined limits in the components' datasheets.

Computer-aided circuit simulators are used to identify the design limits of the device and/or the design limits of the individual components, respectively. Some simulators (e.g., LTspice [1] and PSpice [2]) offer the possibility for a Monte Carlo (MC) analysis. This stochastic analysis provides statistical data on the impact of a device parameter's variance. A major disadvantage of such stochastic methods is that they require a high number of simulation runs to reach the device's design limits

<sup>&</sup>lt;sup>1</sup>The parameters can be constants or variables.

<sup>&</sup>lt;sup>2</sup>Including the ambient conditions during operation (e.g., ambient temperature  $T_A$ ), additional relationships (e.g., f(i) or f(u)), tolerances, and aging.

or the design limits of the individual components. Other simulators (e.g., Saber [3] and Simplorer [4]) provide numerical optimization methods to perform a worst-case analysis. Here also, several simulation runs are required to reach the device's design limits or the design limits of the individual components. This can be advantageously improved by computing currents and voltages analytically.

For an efficient sizing of electronic circuits, the following building blocks are needed:

- the elemental circuit description (of the electronic circuit) and the formulation of the circuit equations;

- a forward solver<sup>3</sup>;

- an optimization method<sup>4</sup>;

- the ranges of the components' parameters<sup>2</sup> needed by the optimization method.

AnSim is the basis of the design tool, containing the proposed analytic forward solver approach, and an optimizer package.<sup>5</sup> AnSim can be used as universally as possible, supports calculation as well as simulation and is notably suitable for parameter studies, optimization and worst-case sizing of small-scale electronic circuits.

Generally, two main concepts can be distinguished between: standard simulators which use complex nonlinear models like SPICE [6] and simulators based on switched networks with piecewise-linear (PWL) models. An overview of the different circuit simulator approaches is provided in Chapter 2.

Further distinction may be made based on the elemental circuit description, the formulation of the circuit equations (network formulation) and the method used for solving the circuit equations (details in Section 1.3).

The special challenges of circuit simulators are as follows:

• convergence problems due to the numerical integration for solving the systems of differential equations. The choice of step size for the numerical integration is a compromise between accuracy (size of data files) and simulation speed;

2

<sup>&</sup>lt;sup>3</sup>A forward solver provides the solution of the state variables and the signals of interest.

<sup>&</sup>lt;sup>4</sup>An optimization method varying the values of the components in a meaningful way to minimize the objective function, to identify the design limits of the device or the design limits of the individual components, respectively.

<sup>&</sup>lt;sup>5</sup>The implemented methods include, e.g., sequential quadratic program (SQP), evolution strategy (1+1) [5], and Monte Carlo (MC) analysis.

- varying the values of the components in a meaningful way to identify the design limits of the device or the design limits of the individual components, respectively; in a few steps even if the worst-case values are not on the bound-aries of the parameters;

- determination of the ranges of the components' parameters.<sup>2</sup>

Design tools for different applications (e.g., DC/DC converters) from different semiconductor companies are also available. These tools mostly support only fixed circuits, the companies' own components, and are very limited in the modeling of the individual components and their parameters.

#### 1.1.1 Standard simulators which use complex nonlinear models

The semiconductor devices are modeled with complex nonlinear models. Generally, numerical methods are used for solving the system of differential equations. As an illustration, a simple p-n junction diode model is shown in (1.1) [6] as it is used in SPICE.

$$I_{\rm D}(V_{\rm D},T) = I_{\rm S}(T) \left( e^{\frac{qV_{\rm D}}{nkT}} - 1 \right)$$

(1.1)

where

- $I_{\rm D}$  diode current

- *I*<sub>S</sub> reverse bias saturation current

- *q* electron charge

- $V_{\rm D}$  voltage across the diode

- *n* emission coefficient

- k Boltzmann constant

- *T* absolute temperature of the p-n junction

The advantage is that the properties (switching behavior) of the real components are well approximated. The disadvantages are, relatively slow simulation speed, convergence problems, large data files and the difficulty in changing only one component property without affecting other component properties. For example, the forward voltage of a p-n junction diode (1.1) is not described in an explicit form. In this simple case, it is possible to solve the forward voltage  $V_D$  from (1.1), but if the model became more complex, then solving for a specific parameter would be more challenging, if possible at all. Therefore, a worst-case forward voltage model (generally referred to as a worst-case parameter model) is difficult to implement.

# 1.1.2 Simulators based on switched networks with piecewise-linear models

The semiconductor devices are modeled with switched networks with piecewiselinear models. The different conditions (states) of the semiconductors are modeled from a set of constant voltage sources, constant current sources, resistances, inductances and capacitances. The nonlinearities of the inductances and capacitances can be addressed by approximating these elements with PWL models, too. The advantages are: simpler models, much faster simulation speed, and the possibility to change only one component property without affecting other component properties, too. The disadvantages are: the exact switching behavior of the semiconductors cannot be modeled, and a control of the individual PWL models (evaluation of the boundary conditions) is required. For example, the forward voltage of a p-n junction diode is modeled as a constant value, and a worst-case parameter model is easy to implement.

#### **1.2** The proposed approach

The proposed analytic forward solver approach (a resource efficient precision transient circuit simulator without a time step for solving the systems of differential equations) uses analytic solution techniques to identify the time-dependent solution of voltages or currents using proper state equations in closed form and has been developed especially for parameter studies, optimization and worst-case sizing of small-scale electronic circuits. Electronic circuits with linear elements, for example, *R*, *C*, *L*, and independent current and voltage sources, can be described by a system of differential equations, introduced and depicted in the following as SubCircuit-Models.<sup>6</sup> Circuits composed of nonlinear elements, such as L(i), C(u), Diodes, MOSFETs, BJTs, and/or PWM controllers are described by piecewise-linear models and denoted in the following as Circuit-Models.<sup>7</sup> For the elemental circuit description, the proposed forward solver approach uses this special Circuit-Model instead of the widely used netlist as used, for example, in SPICE.

The implemented sequential quadratic program (SQP) is used for optimization (finding the best parameter set to minimize the objective function) and identifying

<sup>&</sup>lt;sup>6</sup>A SubCircuit-Model is described in Section 2.2.

<sup>&</sup>lt;sup>7</sup>A Circuit-Model is described in Section 2.3.

the worst-case scenario (the design limits of the device or the design limits of the individual components, respectively). It is found that the worst-case scenario can be obtained with as few solutions to the forward problem as possible by applying an SQP method. The SQP method in combination with the proposed analytic forward solver approach shows that the identification of the worst-case value converges in a few steps even if the worst-case value is not on the boundary of the parameters.

The proposed approach allows for conducting a full search over the parameter space. The ranges of the components' parameters (worst-case parameter model) needed from the SQP method are easy to implement, as explained in Section 1.2.1, and illustrated using an example in Section 1.2.2.

The advantages are:

- the full flexibility in the modeling of the individual components and their parameters referred to as SubCircuit-Models, respectively Circuit-Models;

- the electronic circuit to be simulated can be built from such SubCircuit-Models without the transformation to a state-space model and the final Circuit-Model is only built once and saved;

- simulation results are extremely compact (functions of the state variables and the signals of interest are returned); this creates the opportunity to investigate certain intervals of time in detail without simulating these repeatedly with a smaller step size, as in the case with a numerical solver and can theoretically be stored with arbitrary precision; even with a high number of simulation runs, the generated data remain easy to handle;

- no convergence problems arise because numerical integration for solving the systems of differential equations is not required;

- analytic methods show the potential of more efficient parameter studies; the worst-case scenario can be obtained with as few solutions to the forward problem as possible by applying an SQP method;

- the SQP method in combination with the proposed analytic forward solver approach shows that the identification of the worst-case value converges in a few steps even if the worst-case value is not on the boundary of the parameters.

# **1.2.1** The proposed approach to model the circuit elements' parameters

In many cases, the exact transient current/voltage curves of the semiconductors do not need do be known. To prove the reliability of the electronic circuit instead, the ranges of the parameters are required. Based on this assumption, the stationary behavior of the semiconductors with constant voltage sources, constant current sources, and resistors can be modeled. The range of the parameters depends on the components used in the electronic circuit and the ambient conditions. The worstcase ranges of the components' parameters are needed. To avoid excessive time consuming datasheet interpolations and scalings, a worst-case parameter model is used instead that describes the range of values the circuit element can take.

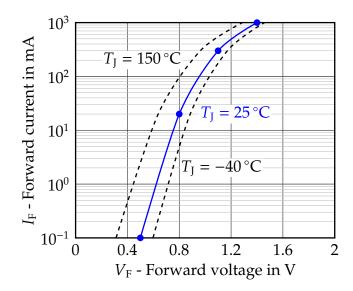

In some cases (e.g., more complex electronic system), the simulation is not the most efficient method (time consuming modeling of the real system); thus, prototyping is the better option. The prototype must be tuned to a worst-case prototype, to guarantee each individual function. Worst-case parameter models are also intended to support the construction of the worst-case prototypes. The procedure for a worst-case parameter model is explained in the following. The forward voltage parameter of a diode is chosen for illustration. The forward voltage characteristics of a general purpose (GP) diode for different junction temperatures  $T_J$ , usually available in the diode's datasheet, are shown in Figure 1.1. The typical forward voltage characteristic  $V_{Ftyp}(I_F)$  is then approximated with piecewise-linear functions (1.2). The support points (marked by blue dots) are drawn in Figure 1.1.

$$V_{\rm F\,typ}(I_{\rm F}, 25\,^{\circ}{\rm C}) = \begin{cases} 0.5, & I_{\rm F} < 0.0001 \\ 0.5 + 15.075\,(I_{\rm F} - 0.0001), & 0.0001 \le I_{\rm F} < 0.02 \\ 0.8 + 3.75\,(I_{\rm F} - 0.02), & 0.02 \le I_{\rm F} < 0.1 \\ 1.1 + 0.333\,(I_{\rm F} - 0.1), & I_{\rm F} \ge 0.1 \end{cases}$$

(1.2)

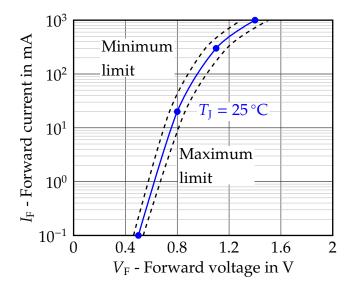

Additionally, the min/max values of  $V_{\rm F}$  are also often provided in a diode datasheet. In all cases, at least the maximum value at one point is given. If only the maximum value is given, the minimum value is evaluated by the tolerance  $C_{\rm TOL} = \left(1 - \frac{V_{\rm Fmax}}{V_{\rm Ftyp}}\right)$ . If not otherwise specified in the diode datasheet, the minimum limit and the maximum limit curves are obtained by scaling the typical curve  $V_{\rm Ftyp}(I_{\rm F}, 25\,^{\circ}{\rm C})$  with the tolerance  $(1 - C_{\rm TOL})$  and  $(1 + C_{\rm TOL})$  respectively, shown in Figure 1.2. The tempera-

Figure 1.1: Illustrated forward voltage characteristic for different junction temperatures  $T_{\rm J}$  of a GP diode.

Figure 1.2: Illustrated forward voltage characteristics with limits of a GP diode.

ture dependency of  $V_{\rm F}$  is considered as an offset  $\Delta V_{{\rm F}T_{\rm J}}$  and is modeled by a constant factor  $C_{\rm TJ} = \left. \frac{\mathrm{d}V_{\rm F}}{\mathrm{d}T_{\rm J}} \right|_{I_{\rm F}={\rm const.}}$  multiplied by  $(T_{\rm J} - 25\,^{\circ}{\rm C})$  and is summarized in (1.3). The factor  $C_{\rm TJ}$  is estimated from the forward characteristics at 25 °C and 150 °C shown in

Figure 1.1 at  $I_F = 0.1 \text{ mA}$ , and is defined by (1.4).

$$\Delta V_{\rm FT_{\rm J}} = C_{\rm TJ} \left( T_{\rm J} - 25 \,^{\circ} {\rm C} \right) \tag{1.3}$$

$$C_{TJ} = \frac{V_{\rm F}(0.0001\,{\rm A}, 25\,^{\circ}{\rm C}) - V_{\rm F}(0.0001\,{\rm A}, 150\,^{\circ}{\rm C})}{25\,^{\circ}{\rm C} - 150\,^{\circ}{\rm C}} = -1.5\,{\rm mV}/^{\circ}{\rm C}$$

(1.4)

Scaling the approximated typical forward voltage (1.2) by the tolerance factor  $(1 + C_{\text{TOL}})$  and adding the temperature dependent part (1.3) results in the final worst-case forward voltage model (equation) as summarized in

$$V_{\rm F}(I_{\rm F}, T_{\rm J}, C_{\rm TOL}) = V_{\rm Ftyp}(I_{\rm F}, 25\,^{\circ}{\rm C})\,(1 + C_{\rm TOL}) + C_{\rm TJ}\,(T_{\rm J} - 25\,^{\circ}{\rm C})\,.$$

(1.5)

#### 1.2.2 Example case worst-case diode forward voltage model

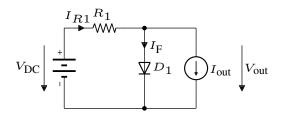

For illustration purposes, the simple voltage reference circuit shown in Figure 1.3 should be sized, by calculation, illustrating the advantages of the analytic solution techniques in combination with worst-case parameter models. The specification is summarized in Table 1.1. For the diode  $D_1$ , the GP diode from the previous Section 1.2.1 is chosen. The self-heating of diode  $D_1$  is neglected (low power dissipation), therefore it follows that  $T_J = T_A$ . Applying Kirchhoff's Current/Voltage Law to the electronic circuit in Figure 1.3 results in (1.6).

| Characteristic                                | Minimum  | Typical | Maximum |

|-----------------------------------------------|----------|---------|---------|

| Product lifetime (operating time) $t_{\rm L}$ | 10 years |         |         |

| Operating temperature range $T_{\rm A}$       | 0°C      | 25 °C   | 60 °C   |

| Input voltage range $V_{\rm DC}$              | 10.8 V   | 12.0 V  | 13.2 V  |

| Output current I <sub>out</sub>               | 80 µA    | 100 µA  | 120 µA  |

| Output voltage $V_{out}$                      | 0.412 V  | 0.512 V | 0.612 V |

Table 1.1: Specification of the simple voltage reference circuit of Figure 1.3.

**Requirements:**

- 1. The resistor  $R_1$  should allow the full range of the output voltage  $V_{out} = V_F$ .

- 2. The design limits of the resistor  $R_1$  ( $R_{1P}$  and  $R_{1VRMS}$ ) and the diode  $D_1$  ( $D_{1VRR}$ ,  $D_{1IF(AV)}$ ,  $D_{1IFR}$ , and  $D_{1TJ}$ ) need to stay below their datasheet limits.

8

Figure 1.3: Simple voltage reference circuit.

$$I_{\rm F} = \frac{(V_{\rm DC} - V_{\rm F}(I_{\rm F}, T_{\rm J}, C_{\rm TOL}))}{R_1} - I_{\rm out}$$

(1.6)

Before the resistor  $R_1$  can be defined, its lower and upper bounds need to be determined. The boundary parameters  $I_{Fmax}$  and  $T_{Jmax}$  as well as  $I_{Fmin}$  and  $T_{Jmin}$ , along with  $\pm C_{TOL}$  are used to determine  $V_{outmin}$  (1.7) and  $V_{outmax}$  (1.8) respectively.

$$V_{\text{out min}} = V_{\text{F}}(I_{\text{Fmax}}, T_{\text{Jmax}}, -C_{\text{TOL}})$$

(1.7)

$$V_{\text{out max}} = V_{\text{F}}(I_{\text{Fmin}}, T_{\text{Jmin}}, C_{\text{TOL}})$$

(1.8)

Then, (1.7) and (1.8) are solved for  $I_{\text{Fmax}}$  and  $I_{\text{Fmin}}$ , respectively, producing  $I_{\text{Fmin}} = 0.153 \text{ mA}$  and  $I_{\text{Fmax}} = 2.466 \text{ mA}$ . Using the boundaries of  $V_{\text{out}}$  from (1.6) instead of  $V_{\text{F}}(I_{\text{F}}, T_{\text{J}}, C_{\text{TOL}})$ , the solutions of  $I_{\text{F}}$  and the worst-case parameter sets (to identify  $R_{1\min}$  and  $R_{1\max}$  respectively) from Table 1.1 results in (1.9) and (1.10).

$$R_{1\min} = \frac{V_{\rm DC\,max} - V_{\rm out\,max}}{I_{\rm F\,min} + I_{\rm out\,min}} = 4.95\,\rm k\Omega \tag{1.9}$$

$$R_{1\max} = \frac{V_{\text{DCmin}} - V_{\text{outmin}}}{I_{\text{Fmax}} + I_{\text{outmax}}} = 37.96 \,\text{k}\Omega \tag{1.10}$$

The value of  $R_1$  can be chosen arbitrarily (no additional requirement e.g., the efficiency of the voltage reference circuit) in the range of  $R_{1 \min} \leq R_1 \leq R_{1 \max}$  and was set to  $12 \text{ k}\Omega \pm 10 \%$ .<sup>8</sup> The maximum power, element voltage, and resistance change of the resistor  $R_1$  are summarized in Table 1.2. The maximum ratings of the GP diode are summarized in Table 1.3. The new boundaries of  $V_{\text{out}}$  are calculated, by using (1.6) with the worst-case parameter sets (to identify  $I_{\text{Fmin}}$  and  $I_{\text{Fmax}}$ , respectively) from Table 1.1 and are described by (1.11)–(1.14).

<sup>&</sup>lt;sup>8</sup>The tolerance of  $R_1$  includes: the resistance basic tolerance (±5%), the resistance change due to temperature (±0.5%), the resistance change due to soldering heat (±0.5%), the resistance change due to aging (±2%, refer  $\Delta R/R$  in Table 1.2), and an additional safety margin of ±2%.

| Table 1.2: Maximum ratings (datasheet parameters) for the resistor $R_1$ and the |

|----------------------------------------------------------------------------------|

| design limits for the simple voltage reference of Figure 1.3.                    |

| Symbol          | Davamatar                                          | Datasheet | Design              |

|-----------------|----------------------------------------------------|-----------|---------------------|

| Symbol          | Parameter                                          | limits    | limits              |

| P <sub>70</sub> | Power rating for $T_A \leq 70 \degree C$           | 0.25 W    | $0.016{ m W}^1$     |

| $V_{\rm RMS}$   | Limiting element voltage                           | 200 V     | 12.8 V <sup>2</sup> |

| $\Delta R/R$    | Max. resistance change at $P_{70}$ after: 225000 h | ±2%       | -                   |

|                 | 2                                                  |           |                     |

${}^{1}R_{1P} = (I_{F\max} + I_{out\max})^{2} R_{1\max} = 0.016 \,\mathrm{W}$

${}^{2}R_{1\,\text{VRMS}} = V_{\text{DC}\,\text{max}} - V_{\text{F}\,\text{min}} = 12.8\,\text{V}$

Table 1.3: Maximum ratings (datasheet parameters) for the GP diode  $D_1$  and the design limits for the simple voltage reference of Figure 1.3.

| Cruchal          | nbol Parameter                          | Datasheet | Design                    |

|------------------|-----------------------------------------|-----------|---------------------------|

| Symbol           |                                         | limits    | limits                    |

| V <sub>RRM</sub> | Peak repetitive reverse voltage         | 50 V      | $\leq 0  \mathrm{V}^1$    |

| $I_{\rm F(AV)}$  | Average rectified forward current       | 1 A       | $1.095  mA^2$             |

| $I_{\rm FRM}$    | Peak repetitive forward current         | 30 A      | $1.095  mA^3$             |

| $T_{\mathrm{J}}$ | Maximum junction temperature            | 175 °C    | $60.1 ^{\circ}\text{C}^4$ |

| $R_{	heta JA}$   | Thermal resistance, junction to ambient | 85 °C/W   | -                         |

${}^{1}D_{1\text{VRR}} \leq 0 \text{ V}$  limited by design.

${}^{2}D_{1 \text{ IF}(AV)} = I_{F \max} = 1.095 \text{ mA}$  ${}^{3}D_{1 \text{ IFR}} = I_{F \max} = 1.095 \text{ mA}$  ${}^{4}D_{1 \text{ TJ}} = T_{A \max} + V_{F \max} I_{F \max} R_{\theta \text{ JA}} = 60.1 \text{ }^{\circ}\text{C}$

$$I_{\rm Fmin} = \frac{(V_{\rm DC\,min} - V_{\rm F}(I_{\rm Fmin}, T_{\rm J\,max}, -C_{\rm TOL}))}{R_{\rm 1max}} - I_{\rm out\,max} = 0.658\,\rm{mA}$$

(1.11)

$$V_{\rm Fmin} = V_{\rm F}(I_{\rm Fmin}, T_{\rm Jmax}, -C_{\rm TOL}) = 0.419\,\rm V$$

(1.12)

$$I_{\rm Fmax} = \frac{(V_{\rm DC\,max} - V_{\rm F}(I_{\rm Fmax}, T_{\rm J\,min}, C_{\rm TOL}))}{R_{\rm 1min}} - I_{\rm out\,min} = 1.095\,\rm{mA}$$

(1.13)

$$V_{\rm Fmax} = V_{\rm F}(I_{\rm Fmax}, T_{\rm Jmin}, C_{\rm TOL}) = 0.59 \,\rm V \tag{1.14}$$

$$I_{\rm Ftyp} = \frac{\left(V_{\rm DC\,typ} - V_{\rm F}(I_{\rm Ftyp}, T_{\rm Jtyp}, 0)\right)}{R_{\rm 1typ}} - I_{\rm out\,typ} = 0.857\,\rm{mA}$$

(1.15)

$$V_{\rm Ftyp} = V_{\rm F}(I_{\rm Ftyp}, T_{\rm Jtyp}, 0) = 0.511 \, {\rm V}$$

(1.16)

Table 1.4: Design limits of *V*<sub>out</sub> of the simple voltage reference circuit of Figure 1.3.

| Characteristic                  | Minimum | Typical | Maximum |

|---------------------------------|---------|---------|---------|

| Output voltage V <sub>out</sub> | 0.419 V | 0.511 V | 0.590 V |

With  $V_{\text{out}} = V_{\text{F}}$  the boundaries for  $V_{\text{out}}$  are:

$V_{\text{out min}} = 0.419 \text{ V}$  and  $V_{\text{out max}} = 0.59 \text{ V}$ .

Additionally, the typical output voltage  $V_{out typ}$  is calculated by (1.15) and (1.16). The boundaries for  $V_{out}$  and the typical output voltage are summarized in Table 1.4. The functionality (requirements) of the simple voltage reference circuit summarized in Table 1.1 was proven. The design limits for the resistor  $R_1$  and the diode  $D_1$  are calculated and summarized in Table 1.2 and in Table 1.3. All its parts, i.e., the resistor  $R_1$  and the GP diode  $D_1$ , are used within their specifications.

# **1.3 State of the art in formulation of the circuit equations**

Computer-aided circuit simulators can be distinguished by three basic features: The first is the elemental circuit description, which can be carried out via a netlist. The second is the formulation of the circuit equations (network formulation) which can, for example, be done with the Nodal Analysis (NA), Modified Nodal Analysis (MNA), or State-space Approach (SSA). The third is the method used for solving the circuit equations.

#### **1.3.1 Standard approach(es)**

An advantage of the widely used NA and MNA [7] is that they can be easily implemented in computer programs for circuit analysis. The algorithm of constructing the set of equations directly from the circuit schematics (netlist) is very simple [8]. NA (1.17) uses Kirchhoff's Current Law for the branch currents at each node in the electronic circuit. The branch constitutive equations (BCE) and Kirchoff's Voltage Law are used to relate the branch currents to branch voltages and the branch voltages

to node voltages, respectively [9].

$$\mathbf{Y}\mathbf{V} = \mathbf{J} \tag{1.17}$$

where

Y nodal admittance matrix

**V** column vector of the node voltages

J column vector of the independent source currents

The disadvantage of the NA method is that, it does not enable analyzing circuits containing voltage sources and elements that lack an admittance matrix, such as transformers [8]. For elements which have no admittance representation, the MNA (1.18) [9] must be used.

$$\underbrace{\begin{bmatrix} \mathbf{Y}_{\mathrm{R}} & \mathbf{B} \\ \mathbf{C} & \mathbf{D} \end{bmatrix}}_{A} \underbrace{\begin{bmatrix} \mathbf{V} \\ \mathbf{I} \end{bmatrix}}_{\mathbf{x}(t)} = \underbrace{\begin{bmatrix} \mathbf{J} \\ \mathbf{F} \end{bmatrix}}_{\mathbf{u}(t)}$$

(1.18)

where

$\mathbf{Y}_{R}$  reduced form of the nodal admittance matrix  $\mathbf{Y}$

**B** matrix represents the contribution to the Kirchoff's Current Law at each node of the additional output or controlling current variables, **I**

V column vector of the node voltages

J column vector of the independent source currents

- **C**, **D** matrices representing the branch constitutive relations, differentiated with respect to the unknown vector

- I column vector of the extra branch currents

- **F** column vector of the independent source voltages

- A MNA matrix

The dynamic MNA equations for the linear case can be written as [10]:

$$\mathbf{G}\mathbf{x}(t) + \mathbf{H}\dot{\mathbf{x}}(t) = \mathbf{u}(t) \tag{1.19}$$

where

- G MNA system matrix

- **H** constant matrix arising from the contributions of all the dynamic *L* and *C* elements

Approaches for solving the NA and MNA (circuit) equations (1.17) and (1.18), respectively, in the time-domain are:

• Several numerical methods exist for solving a system of differential equations

$$\dot{\mathbf{x}}(t) = \mathbf{f}(\mathbf{x}, t), \qquad (1.20)$$

for example, the backward Euler algorithm [11]

$$\mathbf{x}_{n+1} = \mathbf{x}_n + h\mathbf{f}(\mathbf{x}_{n+1}, t_{n+1}), \qquad (1.21)$$

and the trapezoidal algorithm. Applying the backward Euler algorithm to (1.19), the backward Euler solution is summarized in (1.22) where *h* is the step size [12].

$$\mathbf{x}_{n+1} = (\mathbf{H} + h\mathbf{G})^{-1} [\mathbf{H}\mathbf{x}_n + h\mathbf{u}(t_{n+1})]$$

(1.22)

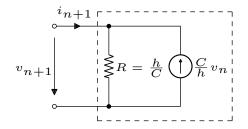

• Alternatively, numerical integration for discrete circuit models for capacitors and inductors can be applied, [11]. In this case, capacitors and inductors are approximated by a resistive circuit<sup>9</sup> in association with the integration algorithm. The discrete circuit associated with the backward Euler algorithm, in the case of a linear capacitor, is shown in Figure 1.4. The current  $i_{n+1}$  through a linear capacitor is approximated using the backward Euler algorithm:

$$i_{n+1} = \frac{C}{h} v_{n+1} - \frac{C}{h} v_n \tag{1.23}$$

Figure 1.4: Discrete circuit models for a linear capacitor, [11].

#### **1.3.2 State-space equation approach**

State-space equations are the smallest possible subset of circuit equations to describe a circuit. The normal matrix form of the state-space model is [8, 11, 13, 14]:

$$\dot{\mathbf{x}}(t) = \mathbf{A}\mathbf{x}(t) + \mathbf{B}\mathbf{u}(t)$$

$$\mathbf{y}(t) = \mathbf{C}\mathbf{x}(t) + \mathbf{D}\mathbf{u}(t)$$

(1.24)

<sup>&</sup>lt;sup>9</sup>The step size divided by the capacitance is seen as a resistance.

where

- $\mathbf{x}(t)$  column vector of state variables

- $\dot{\mathbf{x}}(t)$  column vector of first order derivative of the state variables

- $\mathbf{u}(t)$  column vector of the input

- $\mathbf{y}(t)$  column vector of the output

- A state matrix

- **B** input matrix

- **C** output matrix

- D feedforward matrix

Several methods to obtain the state-space equations from the circuit description are available and can be found, for example, in [8,11,15–18]. Approaches for solving the state-space (circuit) equations (1.24) in the time-domain are:

• numerical integration:

applying the backward Euler algorithm, for example, to (1.24), the backward Euler solution is summarized in (1.25) where *h* is the step size [11].

$$\mathbf{x}_{n+1} = (\mathbf{1} - h\mathbf{A})^{-1} [\mathbf{x}_n + h\mathbf{u}(t_{n+1})]$$

(1.25)

• state-transition matrix:

Closed-form analytic solution of (1.24) (e.g., [11, 14]):

$$\mathbf{x}(t) = \mathbf{\Phi}(t)\mathbf{x}(0) + \int_0^t \mathbf{\Phi}(t-\tau)\mathbf{B}\mathbf{u}(\tau)d\tau$$

(1.26)

where  $\mathbf{\Phi}(t)$  is called the state-transition matrix and is defined by

$$\mathbf{\Phi}(t) = \mathbf{e}^{\mathbf{A}t} \,. \tag{1.27}$$

• Laplace transform (e.g., [11, 14]): the solution for the Laplace transform of (1.24) is

$$\mathbf{X}(s) = \frac{\mathrm{adj}(s\mathbf{I} - \mathbf{A})}{\mathrm{det}(s\mathbf{I} - \mathbf{A})} [\mathbf{x}(0) + \mathbf{BU}(s)].$$

(1.28)

To obtain the time-domain solution, the inverse Laplace transform is used

$$\mathbf{x}(t) = \mathscr{L}^{-1} \left[ \mathbf{X}(s) \right]. \tag{1.29}$$

#### 1.3.3 Other approaches

Other approaches for the formulation of the circuit equations do exist, too. Due to their complexity, respectively their application class, they are not suitable for the analytic forward solver approach (analytic time-domain transient analysis). Still, for the sake of completeness, an overview, including a briefly assessment, is provided.

- The Sparse Tableau Formulation (Tableau Method) [6,8,11–13,19] is a method where all branch currents, all branch voltages, and all nodal voltages are retained as unknowns. Thus, the formulation is most general (everything is available after solution) but leads to large system matrices [12]. Complicated reordering and solution algorithms are necessary to offset the size of the Tableau [6].

- The Hybrid Formulation (Hybrid Method) [6, 11, 13] is a modification of the state-space method, except that the algebraic relationships are not eliminated (no attempt is made to eliminate them in subsequent calculations) [13]. The selection of a network tree is necessary which is a critical part of the formulation algorithm to obtain well-conditioned Hybrid equations [6].

- The Topological Method (Signal Flow) [8, 11, 13, 20] is based on the Mason's formula [20], which constructs the transfer function of a signal flow graph representation of a source node to any other nonsource node [13].

- The Ports Method [13,21] is based on the interconnection and reduction of one and two-port networks. The networks are characterized by their e.g., impedance and admittance [13].

The state-space equation approach has been selected for the formulation of the circuit equations for the analytic forward solver approach, because a closed-form analytic solution (1.26) exists. Additionally, the effort for generating the state-space equation from the elemental circuit description is relative low, which is described in Section 2.1.

#### 1.4 List of publications

The work presented in this thesis has resulted in the following journal publications:

1. **Mario Schenk**, Annette Muetze, and Klaus Krischan, *An analytic approach for resource efficient parametric simulation of electronic circuits*, EPE Journal **30** (2020), no. 1, 33–47.

DOI: https://doi.org/10.1080/09398368.2019.1697077.

Mario Schenk, Annette Muetze, Klaus Krischan, and Christian Magele, Worstcase analysis of electronic circuits based on an analytic forward solver approach, COM-PEL - The international journal for computation and mathematics in electrical and electronic engineering 38 (2019), no. 5, 1655–1666. DOI: https://doi.org/10.1108/COMPEL-12-2018-0531.

#### **1.5 Overview of the thesis**

The introduction of this thesis provides a short overview of the motivation for this work, notably the need for circuit simulators and their unique challenges. The two main concepts of circuit simulators (standard simulators and simulators based on switched networks with piecewise-linear models) are presented. The advantages of the proposed approach are presented as well as the SubCircuit-Models, Circuit-Models (used for the elemental circuit description) and the SQP method (used for optimization and identifying the worst-case scenario). Additionally, the state of the art in formulation of the circuit equations is presented.

**Chapter 2** provides an overview of the different circuit simulator approaches. The basic structure of a SubCircuit-Model of the proposed analytic forward solver approach (for solving electronic circuits) is described. The basic structure of a Circuit-Model and the timedomain transient analysis of the proposed method is presented. The SQP approach for optimization and worst-case analysis of electronic circuits is explained in more detail.

Chapter 3 illustrates the claimed advantages of the proposed closed-form analytic approach with respect to small data file size and CPU time in the case of parameter studies by means of the chosen example case applications, an open-loop and a closed-loop flyback converter. The simulation results obtained from the proposed approach with those of two other simulators as well as experimental results are compared.

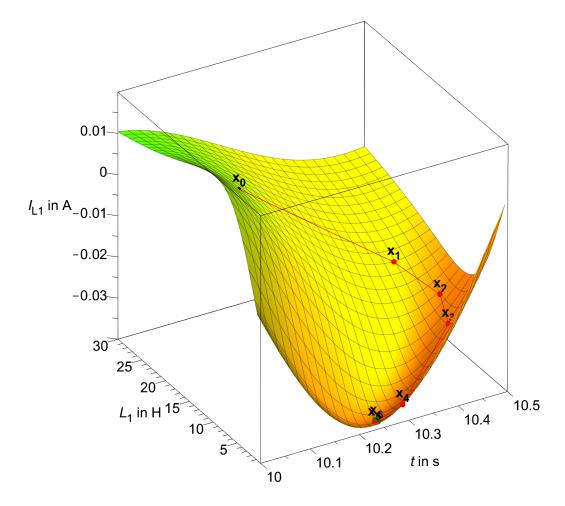

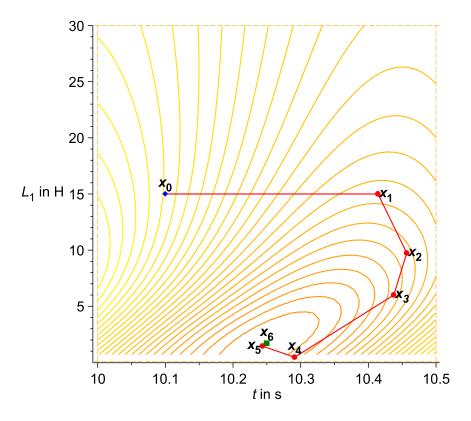

Chapter 4 shows two example case applications of worst-case analyses, an RLC series resonant circuit and a flyback converter in continuous conduction mode. The SQP method in combination with the analytic forward solver approach illustrates that the identification of the worst-case values converges in a few steps even if the worst-case values are not on the boundary of the parameters.

Chapter 5 illustrates a third example case application, the sizing of a step down converter. In contrast to the previous example case applications, first the SQP method is used in combination with the analytic forward solver approach to optimize the efficiency of the step down converter. In the second step, the different components of the step down converter are sized by applying the SQP method in combination with the analytic forward solver approach.

Chapter 6 summarizes this work and also provides an outlook for further investigations.

# Chapter 2

# Analytic forward solver approach for solving electronic circuits

Today, many circuit simulators for electronic circuits with different approaches are available. The proposed approach uses analytic solution techniques and has been developed especially for parameter studies, optimization and identification of the worst-case sizing<sup>1</sup> of small-scale electronic circuits.

The advantages are:

- the full flexibility in the modeling of the individual components and their parameters referred to as SubCircuit-Models, respectively Circuit-Models;

- the electronic circuit to be simulated can be built from such SubCircuit-Models without the transformation to a state-space model and the final Circuit-Model is only built once and saved;

- simulation results are extremely compact (functions of the state variables and the signals of interest are returned); this creates the opportunity to investigate certain intervals of time in detail without simulating these repeatedly with a smaller step size, as in the case with a numerical solver and can theoretically be stored with arbitrary precision; even with a high number of simulation runs, the generated data remain easy to handle;

- no convergence problems arise because numerical integration for solving the systems of differential equations is not required;

- analytic methods show the potential of more efficient parameter studies.

<sup>&</sup>lt;sup>1</sup>Worst-case sizing has been described in Section 1.1.

While a comprehensive review of all existing circuit simulators does not fall within the scope of this thesis, a short overview is provided, for the sake of completion.

Generally, two main concepts can be distinguished between: standard simulators which use complex nonlinear models (e.g., [22-25]) like SPICE [6] along with its multiple derivatives and simulators based on switched networks with piecewise-linear models (e.g., [26–36]). Some of these simulators use simplified piecewise-linear models (e.g., [31, 37, 38]). A method for fast time-domain simulation of networks with switches has been reported [38]. It is based on a discrete-time switch model that consists of a constant conductance in parallel with a current source. The system matrix is constant, independently of the states of the switches. These simulators are much faster than the standard simulators like SPICE (because no iterations over nonlinearities are needed), but at the expense of losing details (e.g., during switching events). The simulators PETS [36] and PECS [30], which support piecewise-linear models, also contain nonlinear elements. The simulator PETS supports smooth nonlinear models using a "delay" approximation [36]. (It is a not iterative method and is presumed faster than but not as accurate as the standard Newton-Raphson method [30]). In contrast to the simulator PECS, nonlinear elements are modeled as equivalent voltage and current sources (updated at every time step and for every nonlinear iteration). The entire circuit is modeled as these equivalent sources connected to a linear time-invariant system during each switching interval. An iterative Newton–Raphson method is used to achieve convergence to high accuracy [30]. Algorithms for solving piecewise-linear networks can be found in [39–46].

Further distinction may be made based on the formulation of the circuit equations: some simulators use state-space equations (SSE) (e.g., [26,27,29–34,45,47–49]) while others use nodal equations (NE) (e.g., [28,50]), or modified nodal equations (MNE) (e.g., [6, 36, 51]). The advantage of the state-space equations in contrast to NE or MNE is that an analytic solution, as described in (1.26), exists. The disadvantage is the additional effort needed for generating the state-space equation from the circuit description.

Furthermore, symbolic simulators like ISAAC [52], SAPWIN [53,54] and Analog Insyde [51] exist. (In the tutorial [55], the basic principles and the scope of application for symbolic computation have been reviewed.) These simulators do not support fully analytic time-domain transient analysis for switched networks with piecewise-linear models. The simulator for integrated switched-mode power supplies circuits (SISMPSC) [26] is based on symbolic calculus tools and supports symbolic

state-space equations (SSSE) but uses numerical methods for solving the systems of ordinary differential equations (ODEs). Analog Insyde is essentially restricted to symbolically-solved linear circuits using the Laplace transform [51]. A method for the simulation of electronic circuits by state variables decoupling (SECSVD) [45] supports analytic closed-form solutions for restricted input excitation functions, but does not support SSSE.

For modeling power electronics systems PLECS [27,56] or GeckoCIRCUITS [28] are frequently used, both of which have their origin at ETH Zurich. Further power electronics simulation tools are available such as Saber [3], Simplorer [4], Portunus [57] and PSIM [58]. Saber and Simplorer are integrated environments for designing and analyzing complex power electronic systems and multi-domain physical systems. Portunus is a system simulator whose applications range from the simulation of drive systems and switched mode power supplies to investigation of the heating of electronic components. PSIM is one of the fastest simulators for power electronics simulation. All these simulators use numerical integration for solving the systems of differential equations. Further interesting references in the context of power electronics modeling can be found in [46,59–66].

The most important characteristics of time-domains simulators are summarized in Table 2.1. The proposed analytic forward solver approach closes the gap between symbolic simulators which do not fully support analytic time-domain transient analysis for switched networks with piecewise-linear models on the one hand, and the none symbolic simulators based on the switched networks with piecewise-linear models which support analytic time-domain transient analysis (summarized in Table 2.1) on the other hand.

| Analytic<br>solution                                   | Piecewise-<br>linear<br>modeling | Formulation | Examples                       |                                                  |

|--------------------------------------------------------|----------------------------------|-------------|--------------------------------|--------------------------------------------------|

| no                                                     | no                               | MNE         | SPICE<br>[ <mark>6</mark> ]    |                                                  |

| no                                                     | yes                              | SSSE        | SISMPSC<br>[ <mark>26</mark> ] | П                                                |

| no                                                     | yes                              | SSE         | PLECS [27]                     | able 2.1: (                                      |

| no                                                     | yes                              | NE          | Gecko-<br>CIRCUITS<br>[50]     | Table 2.1: Comparison of time-domain simulators. |

| partly                                                 | yes                              | SSE         | PECS<br>[30]                   | of time-c                                        |

| no                                                     | yes                              | MNE         | PETS<br>[36]                   | lomain s                                         |

| only<br>linear<br>circuits                             | no                               | MNE         | Analog<br>5] Insyde<br>[51]    | simulators                                       |

| no                                                     | yes                              | MNE         | SWANN<br>[67]                  |                                                  |

| only<br>restricted<br>input<br>excitation<br>functions | yes                              | SSE         | SECSVD Proposec<br>[45] method |                                                  |

| yes                                                    | yes                              | ESSSE       | Proposed<br>method             |                                                  |

Chapter 2 Analytic forward solver approach for solving electronic circuits

### 2.1 Method overview

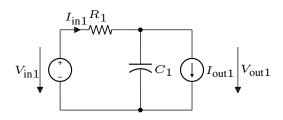

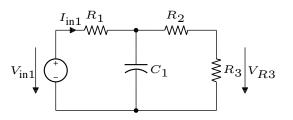

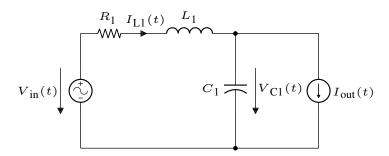

The proposed approach is based on Maple [68], a computer algebra system (CAS). For the elemental circuit description, it uses a special Circuit-Model instead of the widely used netlist as, for example, used in SPICE, Analog Insyde, PECS [30, 69] and SWANN [67]. A Circuit-Model describes the electronic circuit with symbolic ordinary differential equations, if state variables are present. In the case of no state variables, the electronic circuit is described by symbolic algebraic equations. The electronic circuit to be simulated may contain linear and nonlinear components. Linear parts are described directly with a SubCircuit-Model and nonlinear ones with a Circuit-Model which comprises several SubCircuit-Models itself, the associated boundary conditions and a state table. The proposed approach uses SubCircuit-Models for piecewise-linear components. A SubCircuit-Model is an extended symbolic state-space model (ESSSM) in which the SSSM is extended by an I/O interface<sup>2</sup> and some additional information. An example of a SubCircuit-Model is provided in Figure 2.1. The associated ESSSM is described by (2.1)–(2.3). Eq. (2.1) represents the

Figure 2.1: SubCircuit-Model: simple RC-circuit.

ordinary differential equation, (2.2) the signal of interest and (2.3) the I/O interface.

$$C_1 \frac{\mathrm{d}V_{\rm C1}(t)}{\mathrm{d}t} = \frac{V_{\rm in1} - V_{\rm C1}(t)}{R_1} - I_{\rm out1}$$

(2.1)

$$y_1(t) = V_{C1}(t)$$

(2.2)

I/O interface:

$$\mathbf{y}_{\text{IO1}}(t) = \begin{bmatrix} \mathbf{y}_{\text{I1}}(t) \\ \mathbf{y}_{\text{O1}}(t) \end{bmatrix} \quad \text{with} \qquad \mathbf{y}_{\text{I1}}(t) = \begin{bmatrix} \frac{V_{\text{in1}} - V_{\text{C1}}(t)}{R_1} \\ V_{\text{in1}} \end{bmatrix} \qquad \mathbf{y}_{\text{O1}}(t) = \begin{bmatrix} I_{\text{out1}} \\ V_{\text{C1}}(t) \end{bmatrix}$$

(2.3)

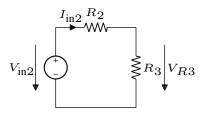

A second example of a SubCircuit-Model, without state variables, is shown in Figure 2.2. In case of no state variables, only (2.4), the signal of interest, and (2.5),

<sup>&</sup>lt;sup>2</sup>The I/O interface is described in Section 2.2.2.

the I/O interface exist. In this example, the output-cell  $y_{O2}(t)$  of the I/O interface is not defined.

Figure 2.2: SubCircuit-Model: simple voltage divider.

$$\mathbf{y}_{2}(t) = V_{\rm R3} = V_{\rm in2} \frac{R_3}{R_2 + R_3}$$

(2.4)

I/O interface:

$$\mathbf{y}_{\text{IO2}}(t) = \begin{bmatrix} \mathbf{y}_{\text{I2}}(t) \\ \mathbf{y}_{\text{O2}}(t) \end{bmatrix} \quad \text{with} \qquad \mathbf{y}_{\text{I2}}(t) = \begin{bmatrix} \frac{V_{\text{in2}}}{R_2 + R_3} \\ V_{\text{in2}} \end{bmatrix} \qquad \mathbf{y}_{\text{O2}}(t) = \begin{bmatrix} \end{bmatrix}$$

(2.5)

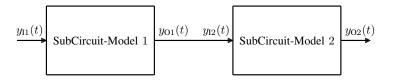

A collection of predefined SubCircuit-Models is provided. Connecting such simple predefined SubCircuit-Models results in a new SubCircuit-Model and is visualized in Figure 2.3. This results in a large number of possible SubCircuit-Models. As mentioned in the introduction in Section 1.2, the approach allows the electronic circuits from SubCircuit-Models to be simulated without the transformation to a state-space model; only the I/O definitions must be substituted, as shown in more detail in Section 2.2.2. This results in a quasi combination of the compact representation of the state-space equations already available and the immediate further use of the modified nodal equations. From the electronic circuit to be simulated, the

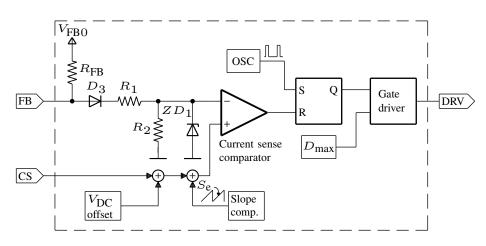

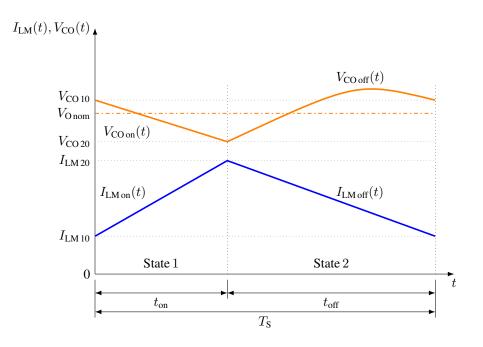

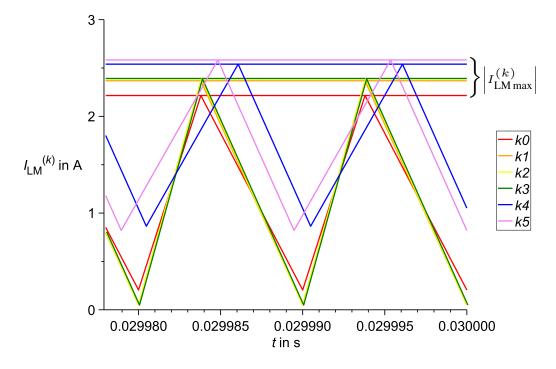

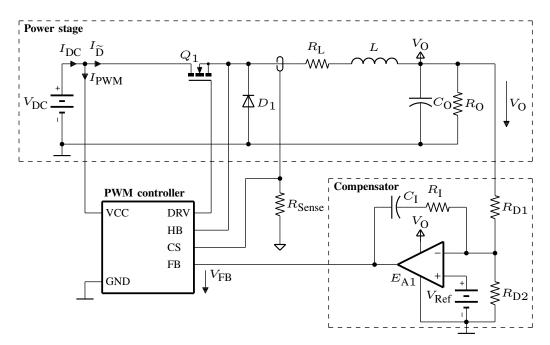

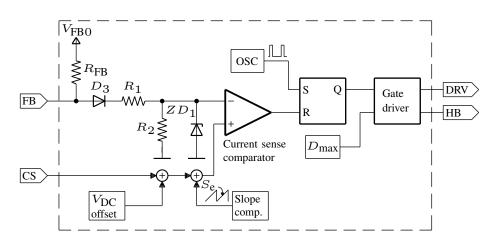

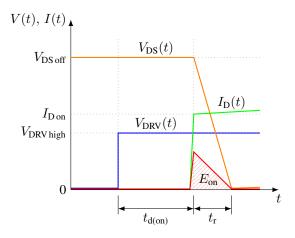

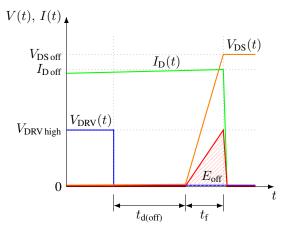

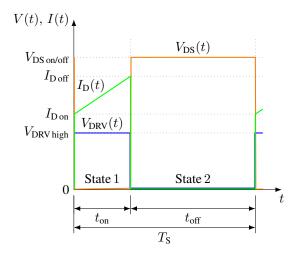

Figure 2.3: Interconnection of two SubCircuit-Models.